Publication # 24850Revision: 3.13Issue Date: February 2005

Advanced Micro Devices 🗖

#### ©2001-2004 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### Trademarks

AMD, the AMD Arrow logo, AMD Athlon, and combinations thereof, are trademarks of Advanced Micro Devices, Inc.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

## Contents

| <b>Revision Hist</b>                                                                                | ory                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 1                                                                                           | Introduction                                                                                                                                                                                                                                                                                                                                  |

| 1.1                                                                                                 | Objective                                                                                                                                                                                                                                                                                                                                     |

| 1.2                                                                                                 | Related Information                                                                                                                                                                                                                                                                                                                           |

| 1.3                                                                                                 | Abbreviations                                                                                                                                                                                                                                                                                                                                 |

| Chapter 2                                                                                           | Processor Package Descriptions                                                                                                                                                                                                                                                                                                                |

| Chapter 3                                                                                           | Socket 754 Design Requirements                                                                                                                                                                                                                                                                                                                |

| 3.1                                                                                                 | Socket 754                                                                                                                                                                                                                                                                                                                                    |

| 3.2                                                                                                 | Base and Cover                                                                                                                                                                                                                                                                                                                                |

| 3.2                                                                                                 | .1 Socket 754 Vendor Marking                                                                                                                                                                                                                                                                                                                  |

| 3.2                                                                                                 | .2 Other Socket 754 Markings                                                                                                                                                                                                                                                                                                                  |

| 3.3                                                                                                 | Socket 754 Contact Material and Plating                                                                                                                                                                                                                                                                                                       |

| Chapter 4                                                                                           | Socket 754 Qualification Requirements                                                                                                                                                                                                                                                                                                         |

| 4.1                                                                                                 | Qualification Test Report                                                                                                                                                                                                                                                                                                                     |

| 4.2                                                                                                 | Testing                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                     |                                                                                                                                                                                                                                                                                                                                               |

| Chapter 5                                                                                           | Documentation Requirements                                                                                                                                                                                                                                                                                                                    |

| Chapter 5<br>Chapter 6                                                                              | Documentation Requirements                                                                                                                                                                                                                                                                                                                    |

| -                                                                                                   | -                                                                                                                                                                                                                                                                                                                                             |

| Chapter 6                                                                                           | Mechanical Test Procedure Conditions and Requirements                                                                                                                                                                                                                                                                                         |

| <b>Chapter 6</b><br>6.1                                                                             | Mechanical Test Procedure Conditions and Requirements                                                                                                                                                                                                                                                                                         |

| Chapter 6<br>6.1<br>Chapter 7                                                                       | Mechanical Test Procedure Conditions and Requirements       .25         Test Matrix       .25         Electrical Qualification Requirements       .31         Fixture       .31                                                                                                                                                               |

| <b>Chapter 6</b><br>6.1<br><b>Chapter 7</b><br>7.1                                                  | Mechanical Test Procedure Conditions and Requirements       .25         Test Matrix       .25         Electrical Qualification Requirements       .31         Fixture       .31         .1       Capacitance And Inductance Matrices       .31                                                                                                |

| Chapter 6<br>6.1<br>Chapter 7<br>7.1<br>7.1                                                         | Mechanical Test Procedure Conditions and Requirements       .25         Test Matrix       .25         Electrical Qualification Requirements       .31         Fixture       .31         .1       Capacitance And Inductance Matrices       .31         .2       Mated Partial Self-Inductance       .32                                       |

| Chapter 6<br>6.1<br>Chapter 7<br>7.1<br>7.1<br>7.1                                                  | Mechanical Test Procedure Conditions and Requirements.25Test Matrix.25Electrical Qualification Requirements.31Fixture.31.1Capacitance And Inductance Matrices.2Mated Partial Self-Inductance.3Mated Loop Inductance.3Mated Loop Inductance                                                                                                    |

| Chapter 6<br>6.1<br>Chapter 7<br>7.1<br>7.1<br>7.1<br>7.1<br>7.1                                    | Mechanical Test Procedure Conditions and Requirements.25Test Matrix.25Electrical Qualification Requirements.31Fixture.31.1Capacitance And Inductance Matrices.2.31.2Mated Partial Self-Inductance.3Mated Loop Inductance.32                                                                                                                   |

| Chapter 6<br>6.1<br>Chapter 7<br>7.1<br>7.1<br>7.1<br>7.1<br>7.1<br>7.1                             | Mechanical Test Procedure Conditions and Requirements.25Test Matrix.25Electrical Qualification Requirements.31Fixture.31.1Capacitance And Inductance Matrices.2Mated Partial Self-Inductance.3Mated Loop Inductance.4Mated Partial Loop Inductance Matrix.3Differential Impedance Definition.34                                               |

| Chapter 6<br>6.1<br>Chapter 7<br>7.1<br>7.1<br>7.1<br>7.1<br>7.1<br>7.1<br>7.1<br>7.2               | Mechanical Test Procedure Conditions and Requirements.25Test Matrix.25Electrical Qualification Requirements.31Fixture.31.1Capacitance And Inductance Matrices.2.31.2Mated Partial Self-Inductance.3Mated Loop Inductance.4Mated Partial Loop Inductance Matrix.32.4Mated Partial Loop Inductance Matrix.34                                    |

| Chapter 6<br>6.1<br>Chapter 7<br>7.1<br>7.1<br>7.1<br>7.1<br>7.1<br>7.1<br>7.2<br>7.2               | Mechanical Test Procedure Conditions and Requirements.25Test Matrix.25Electrical Qualification Requirements.31Fixture.31.1Capacitance And Inductance Matrices.3Mated Partial Self-Inductance.3Mated Loop Inductance.3Mated Partial Loop Inductance Matrix.3.32.4Mated Partial Loop Inductance.31.34.31.34.32.34.34.35                         |

| Chapter 6<br>6.1<br>Chapter 7<br>7.1<br>7.1<br>7.1<br>7.1<br>7.1<br>7.1<br>7.2<br>7.2<br>7.2<br>7.3 | Mechanical Test Procedure Conditions and Requirements.25Test Matrix.25Electrical Qualification Requirements.31Fixture.31.1Capacitance And Inductance Matrices.2Mated Partial Self-Inductance.3Mated Loop Inductance.3Mated Loop Inductance.32.32.4Mated Partial Loop Inductance Matrix.32.34.1Differential Impedance Definition.34.34.35.1.35 |

| 7.4 Propag  | ation Delay Skew                    |

|-------------|-------------------------------------|

| 7.4.1       | Single-Ended Propagation Delay Skew |

| 7.4.2       | Differential Propagation Delay Skew |

| 7.5 Capaci  | tance                               |

| 7.5.1       | Test Procedures                     |

| 7.5.2       | Test Condition                      |

| 7.5.3       | Requirements                        |

| 7.6 Electri | cal Specifications                  |

## **List of Figures**

| Figure 1. | A 3-D View of Socket 754                                                                    | 11  |

|-----------|---------------------------------------------------------------------------------------------|-----|

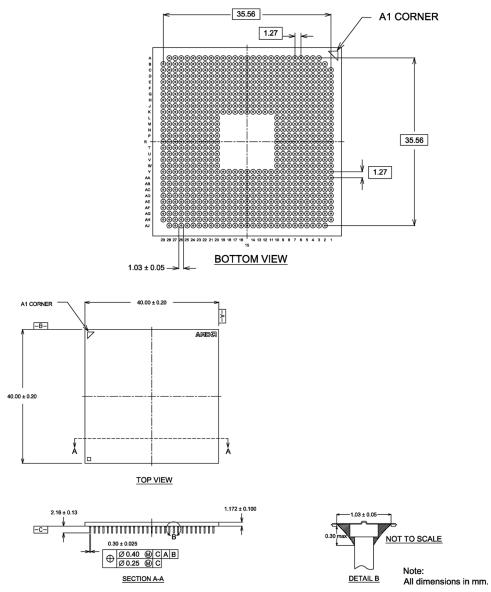

| Figure 2. | 754-Pin μOPGA Package Drawing.                                                              | 15  |

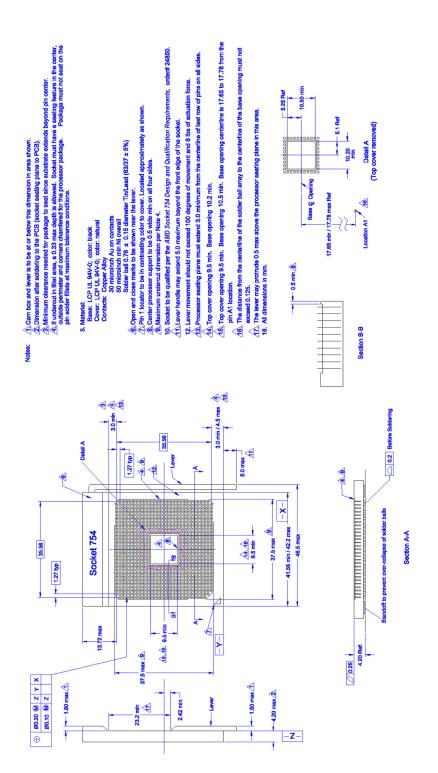

| Figure 3. | Socket 754 Outline                                                                          | 18  |

| Figure 4. | Recommended PCB-Keepout                                                                     | 19  |

| Figure 5. | Socket 754 Qualification Test Matrix                                                        | .25 |

| Figure 6. | Pin Configuration for the Maxwell Capacitance and Partial Inductance Matrix<br>Measurement  | 31  |

| Figure 7. | Loop Measurement for Extracting [LP] for a Mated Three-Pin Combination                      | 33  |

| Figure 8. | Current/Voltage Definitions and Equivalent Circuit of the Partial Loop<br>Inductance Matrix | 33  |

| Figure 9. | Pin Configurations for the Propagation Delay Skew Measurements of<br>Single-Ended Signals   | 36  |

24850 Rev. 3.13 February 2005

Socket 754 Design and Qualification Requirements

## **List of Tables**

| Table 1. | List of Abbreviations.                              | 13 |

|----------|-----------------------------------------------------|----|

| Table 2. | Mechanical Qualification Test Procedures            | 26 |

| Table 3. | Summary of Required Measurements for the Socket 754 | 39 |

## **Revision History**

| Date          | Revision | Description                                                                                           |

|---------------|----------|-------------------------------------------------------------------------------------------------------|

| February 2005 | 3.13     | Corrected specified value for resistance of a single mated pin in Table 3.                            |

| December 2004 | 3.11     | Internal revision                                                                                     |

| November 2004 | 3.09     | Corrected the requirements for Mated Loop Inductance and Mated Partial Loop Inductance.               |

| July 3003     | 3.07     | Corrected the base opening measurements given in Note 14 and Note 15 of Figure 3, Socket 754 Outline. |

| May 2003      | 3.02     | Minor marketing revisions.                                                                            |

## Chapter 1 Introduction

This document defines the Socket 754, shown in Figure 1 as it is intended for use in value and performance desktop and workstation applications using an AMD Athlon<sup>™</sup> 64 processor.

## 1.1 Objective

Socket 754 is a Zero Insertion Force (ZIF) Micro Pin Grid Array ( $\mu$ PGA) Socket using Ball Grid Array (BGA) surface mount technology on 1.27 mm pitch.

#### Figure 1. A 3-D View of Socket 754

Socket 754 dimensional, performance, and qualification testing requirements are defined and designed to ensure that Socket 754 performs to the AMD electrical and mechanical design requirements.

This document includes Socket 754 outline and qualification tests required for a supplier to become qualified by AMD as a Socket 754 vendor. Socket 754 is designed for the AMD product line of microprocessors.

Socket 754 Design and Qualification Requirements

## **1.2 Related Information**

The following documents contain additional information related to the Socket 754 microprocessor:

Note: EIA standards are referenced throughout this document to perform measurements. The EIA

| v           | n Global Engineering can be obtained online at<br>hs.com or by calling 1-800-624-3974.                                                                                                                                                                |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EIA 364–09  | Durability Test Procedure for Electrical Connectors and Contacts                                                                                                                                                                                      |

| EIA 364–11  | Resistance to Solvents Test Procedure for Electrical Connectors and Sockets                                                                                                                                                                           |

| EIA 364–17  | Temperature Life with or without Electrical Load Test Procedure for Electrical Connectors and Sockets                                                                                                                                                 |

| EIA 364–20  | Withstanding Voltage Test Procedure for Electrical Connectors, Sockets, and Coaxial Contacts                                                                                                                                                          |

| EIA 364–21  | Insulation Resistance Test Procedure for Electrical Connectors Sockets and Coaxial Contacts                                                                                                                                                           |

| EIA 364–23  | Low Level Contact Resistance Test Procedure for Electrical Connectors and Sockets                                                                                                                                                                     |

| EIA 364–27  | Mechanical Shock (Specified Pulse) Test Procedure for Electrical Connectors                                                                                                                                                                           |

| EIA 364–28  | Vibration Test Procedure for Electrical Connectors and Sockets                                                                                                                                                                                        |

| EIA 364–30  | Capacitance Test Procedure for Electrical Connectors                                                                                                                                                                                                  |

| EIA 364–31  | Humidity Test Procedure for Electrical Connectors and Sockets                                                                                                                                                                                         |

| EIA 364–32  | Thermal Shock (Temperature Cycling) Test Procedure for Electrical<br>Connectors and Sockets                                                                                                                                                           |

| EIA 364–48  | Test Procedure for Metallic Coating Thickness Measurements of Contacts                                                                                                                                                                                |

| EIA 364–56  | Resistance to Soldering Heat Test Procedure for Electrical Connectors                                                                                                                                                                                 |

| EIA 364–60  | Test Procedure No.60 General Methods for Porosity Testing of Contact<br>Finishes for Electrical Connectors                                                                                                                                            |

| EIA 364–65  | Mixed Flowing Gas EIA 364–70 Temperature Rise Versus Current Test<br>Procedure for Electrical Connectors and Sockets                                                                                                                                  |

| EIA 364–90  | Crosstalk Ratio Test Procedure for Electrical Connectors, Sockets, Cable<br>assemblies or Interconnection Systems EIA 364–103 Propagation Delay Test<br>procedure for Electrical Connectors, Sockets, Cable Assemblies, or<br>Interconnection Systems |

| EIA 364–108 | Impedance, Reflection Coefficient, Return Loss, and VSWR Measured in the<br>Time and Frequency Domain Test Procedure for Electrical Connectors, Cable<br>Assemblies or Interconnection Systems                                                        |

## 1.3 Abbreviations

Table 1 shows a list of abbreviations used in this document.

| Abbreviation | Definition                        |

|--------------|-----------------------------------|

| AMD          | Advanced Micro Devices            |

| EIA          | Electronic Industries Association |

| LCP          | liquid crystal polymer            |

| LLCR         | low level contact resistance      |

| μs           | microsecond                       |

| μBGA         | micro ball grid array             |

| μPGA         | micro pin grid array              |

| MΩ           | mega-ohm                          |

| mA           | milliampere                       |

| mV           | millivolt                         |

| mΩ           | milli-ohm                         |

| μOPGA        | micro organic pin grid array      |

| РСВ          | printed circuit board             |

| ps           | picosecond                        |

| UL           | Underwriters Laboratories         |

Table 1.List of Abbreviations

## Chapter 2 Processor Package Descriptions

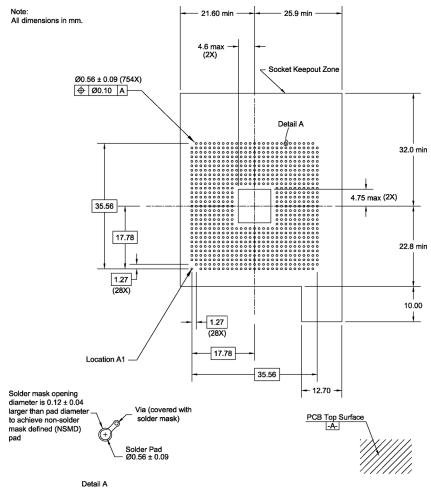

Figure 2 illustrates the 754-pin  $\mu$ OPGA processor package. The Pin A1 designator indicates the Pin A1 location.

Figure 2. 754-Pin µOPGA Package Drawing

*Note:* Socket 754 must be designed so that a 1.95 mm  $\mu$ OPGA package pin length makes full electrical contact.

## Chapter 3 Socket 754 Design Requirements

This chapter shows the design requirements for the Socket 754, including:

- Socket 754

- Base and cover

- Vendor markings

- Other markings

- Contact material and plating

### 3.1 Socket 754

Figure 3 on page 18 illustrates the Socket 754 outline critical dimensions and required notes. The outline also shows the pin A1 designator. The  $\mu$ PGA pin pattern is not symmetrical. The  $\mu$ OPGA processor package inserts only one way into socket 754. The socket 754 does not incorporate tabs for heat sink attachment. Figure 4 on page 19 shows the recommended PCB keepout for Socket 754.

Figure 3. Socket 754 Outline

Figure 4. Recommended PCB-Keepout

### **3.2 Base and Cover**

The Socket 754 base and cover is made of Liquid Crystal Polymer (LCP) with a UL flammability rating of 94V-0. The base color is black and the cover is natural in color.

#### 3.2.1 Socket 754 Vendor Marking

The socket identifier marking, *Socket 754*, must be molded into the CAM box as shown in Figure 3 on page 18. The vendors UL approved trademark identifier and lot traceability number must be positioned on the Socket 754 to allow visibility and readability after soldering it to the printed circuit board (PCB). The lot traceability number can be ink stamped or laser marked.

#### 3.2.2 Other Socket 754 Markings

An open and close designator must be molded into the CAM box in close proximity to the lever handle.

### 3.3 Socket 754 Contact Material and Plating

The contact material must be high-strength copper alloy. Plating must be a minimum 30 micro inches of gold over a minimum 50 micro inches of nickel in the contact area. The solder ball on the bottom side must be  $0.76 \pm 0.15$  millimeter diameter, tin/lead ( $63/37 \pm 5\%$ ). The contact must be plated to create a solder barrier that prevents the solder from wicking up into the contact area during soldering.

## Chapter 4 Socket 754 Qualification Requirements

All qualification testing must be conducted in AMD's designated test facilities. Qualification testing expenses are the responsibility of the Socket 754 supplier. Qualification testing must be performed on production lots of Socket 754.

### 4.1 Qualification Test Report

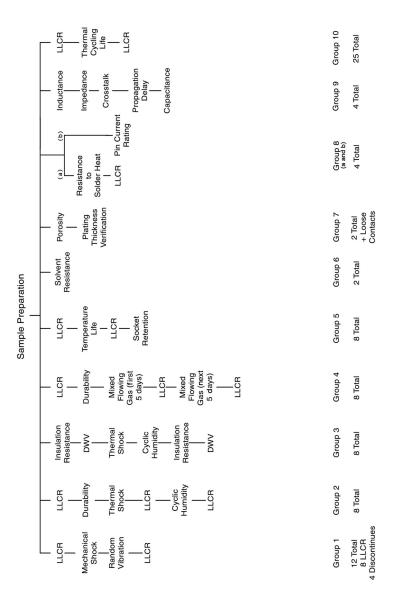

A test report must be written for each test listed in Figure 5 on page 25. All test reports for Groups 1 to 8 and group 10 must be presented in one folder. Group 9 can be presented in a separate folder. The test report must contain the following for each test conducted:

- Title of the test

- Number of specimen and description

- Specimen lot numbers

- Test equipment used and date of both the last and next calibration

- Test procedure, including test method, cycling rate, fixtures used, and number of cycles

- Photographs, sketches, or drawings of the test set-up

- Copy of all raw data taken

- All raw data reduced to tables and/or graphs for clear concise understanding of results

- Statement that all specimens passed all requirements or the number of specimens that failed

- Date of test and name of operator

- Sample calculations to reduce data

- Other data as required in each EIA document

### 4.2 Testing

Please contact the local AMD field applications engineer (FAE) for testing locations. The local AMD FAE can be reached at 1-800-538-8450.

## **Chapter 5 Documentation Requirements**

The supplier of the Socket 754 must submit a minimum amount of documentation to AMD:

- Socket 754 drawing and specifications in supplier's format

- Qualification Test Report (See Section 4.1 on page 21)

- Socket 754 first article inspection report, with the raw data

- Recommended soldering parameters

- Recommended PCB layout guidelines

- Supplier's Part Number for each qualified Socket 754

- Sample of Socket 754 from qualification test lot

The documentation package, as specified in Chapter 5, must be submitted to AMD. If all testing parameters are met, AMD will add the Socket 754 supplier data to the AMD development partners listing.

## Chapter 6 Mechanical Test Procedure Conditions and Requirements

This chapter describes the mechanical test procedure conditions and requirements for the Socket 754.

### 6.1 Test Matrix

Figure 5 shows the Socket 754 qualification matrix.

Figure 5. Socket 754 Qualification Test Matrix

For a Socket 754 to be qualified by AMD it must pass all mechanical requirements listed in Table 2 and Electrical requirements shown in Chapter 7 on page 31, when tested in the sequence listed in Figure 5 on page 25.

| Test Procedure Test Condition         |                                                                                                    | Requirements                                                                                                      |  |  |

|---------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|

| Low Level Contact Resistance (LLCR)   |                                                                                                    |                                                                                                                   |  |  |

| EIA-364-23                            | 100 mA maximum, 20 mV                                                                              | Record Initially                                                                                                  |  |  |

|                                       | 336 contacts (168 contact pairs                                                                    | Calculate single pin LLCR =                                                                                       |  |  |

|                                       | minimum) monitored per test sample                                                                 | Resistance of Pairs - $1m\Omega$                                                                                  |  |  |

|                                       |                                                                                                    | 2                                                                                                                 |  |  |

|                                       |                                                                                                    | After testing, LLCR-per-contact must not exceed 20.0 m $\Omega$ with alloy-194 pins.                              |  |  |

| Mechanical Shock                      |                                                                                                    |                                                                                                                   |  |  |

| EIA 364-27, Cndition A                | 50 G, 11 ms, half-sine                                                                             | No physical damage                                                                                                |  |  |

|                                       | Conducted with 450 g heatsink test<br>mass attached to the retention<br>mechanism and PCB assembly | No contact interruptions greater than 1.0 µs                                                                      |  |  |

| Random Vibration                      |                                                                                                    |                                                                                                                   |  |  |

| EIA 364–28, Condition VII,<br>Level D | 3.1 G rms, 20 to 500 Hz, 15 minutes per axis duration                                              | No physical damage                                                                                                |  |  |

|                                       | Conducted with 450 g heatsink test                                                                 | No contact interruptions greater than                                                                             |  |  |

|                                       | mass attached to the retention<br>mechanism and PCB assembly                                       | 1.0 μs                                                                                                            |  |  |

|                                       |                                                                                                    | LLCR 20.0 m $\Omega$ maximum per contact                                                                          |  |  |

| Durability                            |                                                                                                    |                                                                                                                   |  |  |

| EIA 364-09                            | Fifty cycles per test sample                                                                       | No physical damage                                                                                                |  |  |

|                                       |                                                                                                    | LLCR 20.0 m $\Omega$ maximum per contact                                                                          |  |  |

| Thermal Shock                         |                                                                                                    |                                                                                                                   |  |  |

| EIA-364-32                            | -55°C to + 110°C minutes at each extreme, five cycles                                              | No physical damage                                                                                                |  |  |

|                                       | Group 2 samples exposed to the environment mated                                                   | Group 2—LLCR 20.0 m $\Omega$ maximum per contact                                                                  |  |  |

|                                       | Group 3 samples exposed to the environment unmated                                                 | Group 3—Insulation resistance 1000 $M\Omega$ minimum then DWV 650 VAC (See IR and DWV test procedures on page 27) |  |  |

Table 2.

Mechanical Qualification Test Procedures

| <b>Test Procedure</b>                | Test Condition                                             |                 | Requirements                                                                                               |  |

|--------------------------------------|------------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------|--|

| Cyclic Humidity                      |                                                            |                 |                                                                                                            |  |

| EIA 364-31 Method III Condition<br>C | 25 to 65°C, at 90 to 95% relative humidity                 |                 | No physical damage                                                                                         |  |

|                                      | Group 2 samples exposed to the environment maged           |                 | Group 2—LLCR – 20.0 m $\Omega$ maximum per contact measured at 250 and 504 hours)                          |  |

|                                      | Group 3 samples exposed to the environment unmated         |                 | Group 3—Insulation resistance 1000<br>M minimum then DWV 400 Vac (See<br>IR and DWV test procedures below) |  |

| Insulation Resistance (IR)           |                                                            |                 |                                                                                                            |  |

| EIA 364-21                           | 20 Adjacent contacts, 50                                   | 00 Vdc          | 1000 MΩ minimum                                                                                            |  |

| Dielectric Wistanding Voltage (I     | OWV)                                                       |                 |                                                                                                            |  |

| EIA 364-20                           | 20 Adjacent contacts, 65                                   | 50 VAC          | No breakdown, flashover, arcing, etc.                                                                      |  |

| Mixed Flowing Gas                    |                                                            |                 |                                                                                                            |  |

| EIA 364-65 Condition IIA             | Chlorine                                                   | 10 ppb          | No physical damage                                                                                         |  |

|                                      | Hydrogen Sulfide                                           | 10 ppb          | LLCR 20.0 m $\Omega$ maximum per contact                                                                   |  |

|                                      | Nitrogen Dioxide                                           | 200 ppb         |                                                                                                            |  |

|                                      | Sulfur Dioxide                                             | 100 ppb         |                                                                                                            |  |

|                                      | Temperature                                                | 30°C            |                                                                                                            |  |

|                                      | Relative Humidity                                          | 70 %            |                                                                                                            |  |

|                                      | Duration 10 days total:                                    |                 |                                                                                                            |  |

|                                      | First five days on half samples mated and one-half unmated |                 |                                                                                                            |  |

|                                      | Second five days all san                                   | nples are mated |                                                                                                            |  |

| Temperature Life                     |                                                            |                 |                                                                                                            |  |

| EIA 364-17 Method A                  | +115°C, 432 hours                                          |                 | No physical damage                                                                                         |  |

|                                      |                                                            |                 | LLCR 20.0 m $\Omega$ maximum per contact (measured at 250 and 432 hours)                                   |  |

| Solvant Resistance                   |                                                            |                 |                                                                                                            |  |

| EIA 364-11                           | Four Solution Test in Table 1 of EIA-<br>364-11            |                 | No physical damage and markings are legible                                                                |  |

#### Table 2. Mechanical Qualification Test Procedures (Continued)

I

| <b>Test Procedure</b>      | Test Condition                                                                                      | Requirements                                                                                          |  |

|----------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|

| Socket Retention           |                                                                                                     |                                                                                                       |  |

|                            | Clamp Socket 754 so that a µPGA package can be inserted.                                            | Extraction force must be 8 kg minimum                                                                 |  |

|                            | Place a µPGA package in the clamped<br>Socket 754, then close and lock the<br>socket.               | Record the forces required                                                                            |  |

|                            | With Socket 754 locked, pull the $\mu$ PGA package out of the socket and record the force required. |                                                                                                       |  |

| Porosity (Gold Contacts On | ly)                                                                                                 |                                                                                                       |  |

| EIA 364-60                 | Test loose contacts (quantity of 20)                                                                | Count and record pores                                                                                |  |

|                            | Procedure 1.1.1 (Au/Ni): Nitric Acid<br>Technique                                                   |                                                                                                       |  |

| Plating Thickness          |                                                                                                     |                                                                                                       |  |

| EIA 364-48 Method C        | twenty contacts-measure the gold and nickel thickness.                                              | 30 microinch min–Gold<br>50 microinch min–Nickel                                                      |  |

|                            | Thickness may be measured by X-ray, florescence, or cross sectioning                                |                                                                                                       |  |

| Resistance to Solder Heat  |                                                                                                     |                                                                                                       |  |

| EIA 364-56                 | Solder the Socket 754 to the PCB using                                                              | No physical damage                                                                                    |  |

|                            | convection reflow<br>Reflow the assembly three times                                                | Specify reflow soldering, solder stencil<br>parameters and solder paste percentage<br>of tin and lead |  |

|                            |                                                                                                     | Measure after three passes through reflow                                                             |  |

|                            |                                                                                                     | Flatness per Figure 3 on page 18,<br>Section A-A before and after soldering                           |  |

|                            |                                                                                                     | LLCR 20.0 m $\Omega$ maximum per contact                                                              |  |

#### Table 2. Mechanical Qualification Test Procedures (Continued)

| <b>Test Procedure</b> | Test Condition                                                                                                     | Requirements                                                            |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|

| Pin Current Rating    |                                                                                                                    |                                                                         |  |

| EIA 364-70 Method 2   | The 330 contacts must be connected in series.                                                                      | Generate graph Temperature Rise vs.<br>Current.                         |  |

|                       | Place thermocouple under Socket 754 between pins (P22, P23, R22, and                                               | 1.5 Amp per pin at T – rise of 20°C max.                                |  |

|                       | R23).<br>Supply 12 V to the fan when testing.                                                                      | Continue testing until delta T – rise is 30°C.                          |  |

| Thermal Cycling Life  |                                                                                                                    |                                                                         |  |

| EIA 364-32            | Sample size 25 minimum                                                                                             | No physical damage                                                      |  |

|                       | Apply the temperature cycle with the<br>retention mechanism load applied, then<br>remove the applied load for each | LLCR 20.0 mΩ max. per contact over 336 contacts (168 pin pairs)         |  |

|                       | LLCR measurement.<br>-55°C to 110°C, (temperature $\pm$ 5°C                                                        | Measure LLCR each 250 cycles until failure                              |  |

|                       | Solder Ball Temperature<br>Maximum of 2 cycles per hour                                                            | A socket has failed if one contact exceeds the 20.0 m $\Omega$ maximum  |  |

|                       | Once the solder ball junction reaches<br>the temperature specified, soak for 5<br>minutes                          | Record LLCR measurements unti 60% of the sockets have a failure or 3000 |  |

|                       | The chamber temperature may be<br>raised or lowered to speed the<br>temperature change at the solder ball          | cycles are completed<br>Occurance of 1000 cycles minimum                |  |

|                       | All samples shall be mated during testing                                                                          | with no failures                                                        |  |

#### Table 2. Mechanical Qualification Test Procedures (Continued)

I

## **Chapter 7** Electrical Qualification Requirements

This chapter describes the fixture, inductance, differential impedance, differential and single ended crosstalk, propagation delay skew, capacitance, and a summary of electrical measurement requirements for the Socket 754.

### 7.1 Fixture

All test fixtures that are required to conduct the electrical qualification requirements will be furnished by AMD to the AMD-designated testing facility.

#### 7.1.1 Capacitance And Inductance Matrices

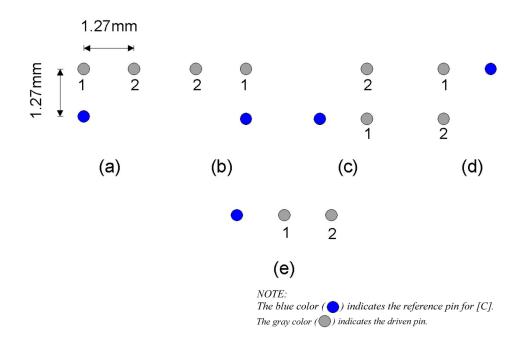

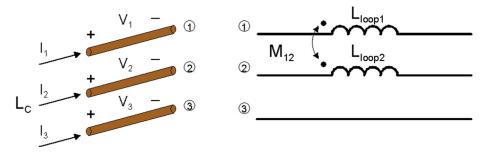

The partial "loop" inductance and Maxwell capacitance matrices, (see Section 7.4 on page 35, for definitions), are measured for the three mated pin configurations shown in Figure 6. For the pin configurations, the Maxwell capacitance matrix and the partial "loop" inductance matrix are of equal size, both are 2 x 2.

#### Figure 6. Pin Configuration for the Maxwell Capacitance and Partial Inductance Matrix Measurement

#### 7.1.2 Mated Partial Self-Inductance

The following procedures are required to properly test for mated partial self-inductance.

#### 7.1.2.1 Test Procedure

Use a validated "industry-standard" 3-D EM field solver. This is the only quantity in the specification that need not be measured. Values obtained from an accurate, detailed 3-D EM field solver model are acceptable. Do not use this computed quantity in any calculations involving measured data.

#### 7.1.2.2 Test Condition

- Test frequencies are 500 MHz and 2 GHz.

- Use a validated "industry standard" 3-D EM field solver.

- Do not use the computed data in any calculations involving measured data.

#### 7.1.2.3 Requirements

L

Mated, partial self-inductance is 4 nH maximum, assuming the current return is at infinity.

#### 7.1.3 Mated Loop Inductance

The following procedures are required to properly test for mated-loop inductance.

#### 7.1.3.1 Test Procedure

The inductance of a loop is formed by a pair of pins. All current is injected in one pin and returned through the other. Read the values from the Smith chart at the specified frequencies using one port measurement on a vector network analyzer.

#### 7.1.3.2 Test Condition

- Test frequencies: 10 MHz (or 500 MHz) and 2 GHz

- See Figure 6 on page 31 for pin placement

#### 7.1.3.3 Requirements

Mated-loop inductance shall be 3.3 nH maximum using two nearest pins with current in one pin and return in the other pin. Record all pin pattern readings, but use only the nearest neighbors for qualification.

#### 7.1.4 Mated Partial Loop Inductance Matrix

The following procedures are required to properly test for mated partial loop inductance from measured mated loop inductance data.

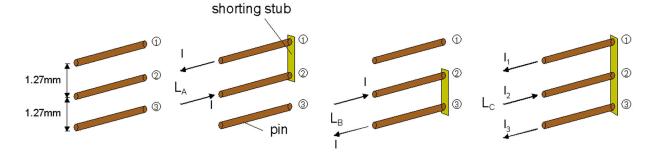

Figure 7 on page 33 shows the loop measurement for extracting  $[L_P]$  for a mated three-pin combination.

Figure 7. Loop Measurement for Extracting [L<sub>P</sub>] for a Mated Three-Pin Combination

Figure 8. Current/Voltage Definitions and Equivalent Circuit of the Partial Loop Inductance Matrix

#### 7.1.4.1 Test Procedure

As shown in Figure 7, the partial inductance matrix of a mated three-pin combination that is extracted from a mated two-pin loop inductance measurements with one of the pins used as the reference (current return). Use the formula in Equation (1) to calculate the mated partial-loop inductance from measured mated-loop inductance data.

$$M_{12} = \frac{L_{loop1} + L_{loop2} - L_{loop3}}{2}$$

(1)

#### 7.1.4.2 Test Condition

Test frequencies are 500 MHz and 2 GHz.

#### 7.1.4.3 Requirements

- M < 3.3 nH max—three-pin loop with one pin used as reference.

- Measurement of the off diagonal entries in the loop partial inductance matrix.

- Diagonal entries of this matrix correspond to Mated Loop Inductance and must meet specified values in Section 7.1.3.3 on page 32.

### 7.2 Differential Impedance Definition

If the dimensions of the socket pins and the spacing between them are small compared to the wavelength of the highest frequency component of interest, then the impedance of the three-pin configuration shown in Figure 6 on page 31 and Figure 8 on page 33 can be calculated approximately from the lumped loop inductance and Maxwell capacitance matrices. When pins 1 and 2 in (Figure 8 on page 33) are driven differentially, with pin 3 acting as ground, then the differential impedance of the transmission line formed by this pin configuration is given by

$$Z_{diff} = 2\sqrt{\frac{L_{loop} - M_{12}}{C + C_{12}}}$$

(2)

#### 7.2.1 Differential Impedance

The following procedures are required to properly test for differential impedance.

#### 7.2.1.1 Test Procedure

- Use the procedures shown in EIA Standard EIA-364-108 or see the equations in terms of partial loop inductance and Maxwell capacitance matrices. If the time domain method is used in measurement, then the signal should have rise time of 35 ps to 150 ps for signal amplitude to go from 10% to 90%.

- The differential transmission line impedance for three mated pins, using one pin as the voltage/ current reference.

- Any frequency domain test equipment recommended in EIA Standard EIA-364-108 may be used to perform the measurements.

- If used, time domain equipment should have sufficient sampling rates to resolve the specified frequencies.

#### 7.2.1.2 Test Condition

- When frequency or time domain methods are used:

- Time domain method uses a Rise Time: 35 ps to 150 ps, 10% to 90%

- For frequency domain method use 500 MHz and 2 GHz

• The differential impedance measured for a three-pin configuration (S1, S2, G).

#### 7.2.1.3 Requirements

The acceptable range for differential impedance is  $100 \pm 10\% \Omega$  with an additional  $\pm 2-\Omega$  measurement error.

### 7.3 Differential and Single-Ended Crosstalk

The following procedures are required to properly test for crosstalk.

#### 7.3.1 Test Procedure

Use the procedures shown in EIA Standard EIA 364–90, Method A or B, for the definitions of crosstalk in terms of the elements of the measured  $\begin{bmatrix} L & partial \\ loop \end{bmatrix}$  and Maxwell capacitance matrices.

#### **7.3.2** Test Condition

- When frequency or time domain methods are used:

- For time domain method use rise time 35 ps to 150 ps, 10% to 90%

- For frequency domain method use 500 MHz and 2 GHz.

- For measurements performed for specified pin pattern differential in Figure 6 on page 31 and to single-ended in Figure 9 on page 36 that include the minimum, the nearest, and the next-to-nearest neighboring pins.

#### 7.3.3 Requirements

Recording crosstalk is recommended to serve as an accuracy check for the partial-loop inductance  $\begin{bmatrix} L & partial \\ loop \end{bmatrix}$  and the Maxwell capacitance matrices.

### 7.4 **Propagation Delay Skew**

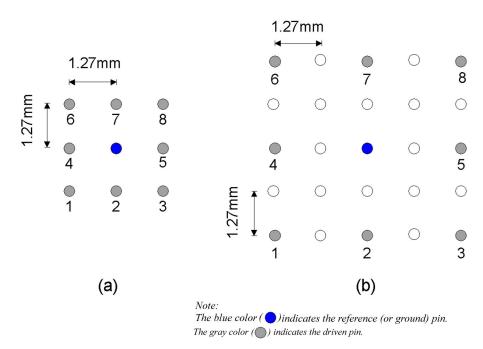

The propagation delay skew for single-ended signal pins is to be measured for the pin configurations shown in Figure 9.

## Figure 9. Pin Configurations for the Propagation Delay Skew Measurements of Single-Ended Signals

Each measurement consists of driving one (gray-shaded) pin as signal and using the center pin (blue) as return. The propagation delay skew for all signal pins in Figure 9(a) are measured. The maximum allowable deviation for all the pins in the array must be less than the specified value. An identical set of measurements must also be repeted for the pin array shown in Figure 9(b).

The differential propagation delay skew is measured for every pin configuration shown in Figure 6 on page 31. In each measurement the two gray-shaded pins (denoted 1 and 2) are driven as signals in differential form, using the blue pin as ground. The maximum allowable deviation in the propagation delay skew for all specified pin configurations must be less than the specified value.

#### 7.4.1 Single-Ended Propagation Delay Skew

The following procedures are required to properly test for single-ended propagation delay.

#### 7.4.1.1 Test Procedure

Propagation delay skew can also be measured using a time delay reflectometer (TDR) by launching the signals through the designated pins, such as those in Figure 9. The signals are launched from the interpposer and the delay skew is observed at the test board. The difference in the propagation times (delay skew) through different pins in the socket can be clearly seen and measured at the open-circuit end of the test board.

**Note:** TDR measurement must account for the two-way trip of the signal DelaySkew =  $\frac{TDR \ Readings}{2}$

#### 7.4.1.2 Test Condition

For the time domain method:

- Time delay of single-ended signals between the top pads of the interposer and the pads on the bottom side fixture.

- The ground return for the specified signal pin pattern of single-ended signals is to be located as specified

#### 7.4.1.3 Requirements

Use the following requirements for measuring delta delay (skew).

- Delta delay (skew) among single-ended pins between the top of the µPGA package and PCB under the Socket 754 must be 10 ps maximum plus 3 ps maximum measurement error.

- Using three pins (S1, S2, and G) for this measurement is recommended.

#### 7.4.2 Differential Propagation Delay Skew

The following procedures are required to properly test for differential propagation delay skew.

#### 7.4.2.1 Test Procedure

Use the procedures shown in EIA Standard EIA-364–103 and in Section 7.4.1.1 on page 36.

#### 7.4.2.2 Test Condition

For the time domain method, the time delay of a differential signal between the top pads of the interposer and the pads on the bottom side of the fixture.

#### 7.4.2.3 Requirements

Use the following requirements for measuring delta delay (skew).

- Delta delay (skew) of a differential signal between the top of the  $\mu$ PGA package and the PCB under the Socket 754, must be 10 ps maximum plus 3 ps maximum measurement error.

- Using three pins (S1, S2, and G) for this measurement is recommended.

### 7.5 Capacitance

At low frequencies, the measurement of the capacitance should be carried out according to the EIA Standard EIA-364-30. Two types of measurements are required—single capacitance between the two nearest pins that are separated by 1.27mm and Maxwell capacitance matrix for multiple pins.

#### 7.5.1 Test Procedures

Use the procedures shown in the EIA Standard, EIA-364-30 and section 7.1.3.1 on page 32.

#### **7.5.2** Test Condition

The following conditions must be met for testing the Socket 754.

• Test Frequencies are 500 MHz and 2 GHz.

Note: Do not short pins for this test.

• The matrix is defined as the Maxwell (not circuit) capacitance matrix.

#### 7.5.3 Requirements

Use the following requirements for measuring capacitance.

- The mated capacitance matrix of any two adjacent pins is 1 pF maximum.

- Measure from the top or bottom of the socket.

- Mated capacitance of three neighboring pins is 1 pF maximum.

- The Maxwell capacitance matrix is measured for a specified, mated three-pin configuration.

- The capacitance matrix of three neighboring pins that are in the same pattern as those used to extract the mated partial inductance matrix.

### 7.6 Electrical Specifications

Table 3 on page 39 contains a summary of the electrical parameter specification for Socket 754. The specifications do not include the effects of the fixtures.

*Note: Proper calibration should be used to de-embed the parasitic contributions for the fixture of the specified electrical parameter.*

| Measured Quantity                                                                                                                                                                                                                       | Definition                                                                                                                                                                                                         | Specified Value(s)                                                                                                                                                                                                                  | Measurement                                                                                                                                                                                 | Applicable<br>Standard                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mated partial self-<br>inductance of a single<br>pin<br>This is the only quantity<br>in the specification that<br>need not be measured.<br>Values obtained from an<br>accurate detailed 3-D<br>EM field solver model<br>are acceptable. | Partial self-<br>inductance of a<br>single mated<br>(interposer-socket<br>combination) pin<br>that is calculated<br>using a 3-D EM<br>field solver                                                                 | Four nH maximum<br>(assuming the<br>current return at<br>infinity)                                                                                                                                                                  | This quantity cannot<br>be measured directly<br>nor can it be calculated<br>uniquely from the<br>measurements.                                                                              | See, Section 7.1.2,<br>"Mated Partial Self-<br>Inductance" on<br>page 32 for the<br>discussion on the<br>mated self-partial<br>inductance.<br>Use a validated<br>industry-standard 3D<br>EM field solver.<br>This computed<br>quantity <i>must not be</i><br>used in any<br>calculations<br>involving measured<br>data.                                                               |

| Mated loop inductance<br>of two nearest pins (i.e.,<br>pins separated by<br>shortest distance)                                                                                                                                          | The inductance of a<br>loop formed by two<br>nearest mated pins.<br>All current is<br>injected into one<br>pin and returned<br>through the other.                                                                  | 3.3 nH maximum                                                                                                                                                                                                                      | The inductance of a<br>loop formed by two<br>nearest pins, which are<br>shorted at the bottom<br>of the socket, with<br>current injected into<br>one pin and returned<br>through the other. | See Section 7.1.3,<br>"Mated Loop<br>Inductance" on<br>page 32 for specified<br>pin configurations.                                                                                                                                                                                                                                                                                   |

| Mated partial loop<br>inductance matrix<br>$\left[L_{loop}^{partial}\right]$ of three<br>neighboring pins                                                                                                                               | Partial inductance<br>matrix of a mated<br>three-pin<br>combination<br>extracted from<br>mated two-pin<br>loop- inductance<br>measurements.<br>One of the pins is<br>used as the<br>reference (current<br>return). | $L_{loop}$ 3.3 nH<br>maximum<br>These are the<br>diagonal entries in<br>the "loop" partial<br>inductance matrix.<br>$M_{12} < 2$ nH ± 10%.<br>These are the off-<br>diagonal entries in<br>the "loop" partial<br>inductance matrix. | The partial inductance<br>matrix is extracted<br>from a series of two-<br>pin loop inductance<br>measurements (as<br>described above) for<br>specified three-pin<br>configurations.         | See Section 7.1.4,<br>"Mated Partial Loop<br>Inductance Matrix"<br>on page 32 for the<br>definition of this<br>matrix and the<br>measurements that<br>should be used to<br>back-calculate the<br>self and mutual<br>partial "loop"<br>inductances.<br>Use the formulas in<br>Section 7.1.4,<br>"Mated Partial Loop<br>Inductance Matrix"<br>on page 32,<br>Equation (1) on<br>page 33 |

| Table 3. | Summary of Required Measurements for the Socket 754 |

|----------|-----------------------------------------------------|

|----------|-----------------------------------------------------|

I

| Measured Quantity                                                                                                                       | Definition                                                                                                                                                       | Specified Value(s)                                                        | Measurement                                                                                                                                                                                                                                                                                                                            | Applicable<br>Standard                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mated capacitance<br>between two nearest<br>pins (i.e., pins separated<br>by shortest distance)                                         | The capacitance<br>between two<br>nearest mated pins                                                                                                             | One pF max                                                                | Capacitance between<br>two nearest pins<br>measured from the top<br>or bottom side of the<br>socket. The pins are<br>not to be shorted<br>together for this<br>measurement.                                                                                                                                                            | Use the EIA-364-30<br>standard for low<br>frequency (10 MHz)<br>measurements. Or,<br>use the network<br>analyzer for S-<br>parameter<br>measurements with<br>minimum frequency<br>of 500 MHz or<br>lower. See Section<br>7.5.1 "Test<br>Procedures" on<br>page 38,                                                                                          |

| Mated capacitance<br>matrix of three<br>neighboring pins<br>The matrix is defined as<br>the Maxwell (not circuit)<br>capacitance matrix | The capacitance<br>matrix of three<br>neighboring pins<br>that are in the same<br>pattern as those<br>used to extract the<br>mated partial<br>inductance matrix. | All entries in the<br>matrix should not<br>exceed 1pF.                    | The Maxwell<br>capacitance matrix<br>measured for the<br>specified mated three-<br>pin configurations.<br><i>Note:</i> The pins are not to<br>be shorted<br>together for this<br>measurement.                                                                                                                                          | Use the EIA-364-30<br>standard for low<br>frequency (10MHz)<br>measurements. Or,<br>use the network<br>analyzer for S-<br>parameter<br>measurements with<br>minimum frequency<br>of 500 MHz or<br>lower. See Section<br>7.5.1 "Test<br>Procedures" on<br>page 38.                                                                                           |

| Differential impedance<br>between two nearest<br>pins (i.e., pins separated<br>by shortest distance)                                    | The transmission<br>line impedance of<br>the odd mode for<br>three mated pins,<br>using one pin as the<br>voltage/current<br>reference.                          | $100 \Omega \pm 10\%$ with an additional $\pm 2-\Omega$ measurement error | The differential (or an odd mode) impedance measured for a three-<br>pin configuration (S1, S2, G).<br>If equipment permits, this quantity may be measured directly. If not, it can be calculated from the measured mated partial "loop" inductance and Maxwell capacitance matrices according to equations provided in this document. | Use the EIA-364-108<br>standard or see the<br>equations in terms of<br>partial inductance<br>and Maxwell<br>capacitance matrices,<br>Section 7.5<br>"Capacitance" on<br>page 37 .<br>If the time domain<br>method is used in<br>measurement, then<br>the signal should<br>have rise time of 35<br>to 150 ps for signal<br>amplitude to go from<br>10 - 90%. |

#### Table 3. Summary of Required Measurements for the Socket 754 (Continued)

| Measured Quantity                                             | Definition                                                                                                                              | Specified Value(s)                               | Measurement                                                                                                                                                                                                                                                   | Applicable<br>Standard                                                                                                                                                                                                                                |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Propagation delay skew<br>among single ended<br>signals.      | Deviation in the<br>propagation delay<br>skew of a single<br>ended signal<br>through different<br>mated (single) pins<br>in the socket. | Ten ps max plus 3 ps<br>max measurement<br>error | Time delay of single<br>ended signal between<br>the top pads of the<br>interposer and the pads<br>on the bottom side<br>fixture.<br>The ground return for<br>the specified signal pin<br>pattern of single ended<br>signals is to be located<br>as specified. | Use EIA-364-103<br>standard or provided<br>in Section 7.4.1.1<br>"Test Procedure" on<br>page 36.<br>See Figure 6 on<br>page 31 for specified<br>signal pin patterns,<br>which also include<br>the location of the<br>current return pin.              |

| Propagation delay skew<br>among differential signal<br>pairs. | Deviation in the<br>propagation delay<br>skew of a single<br>ended signal<br>through mated pin<br>pairs in the socket.                  | Ten ps max plus 3 ps<br>max measurement<br>error | Time delay of a<br>differential signal<br>between the top pads<br>of the interposer and<br>the pads on the bottom<br>side of the fixture. The<br>specified three-pin<br>(S1, S2, G)<br>arrangement should be<br>used.                                         | Use EIA-364-103<br>standard or provided<br>in Section 7.4.1.1<br>"Test Procedure" on<br>page 36. See<br>Figure 6 on page 31<br>for specified<br>differential pin-pair<br>patterns, which also<br>include the location<br>of the current return<br>pin |

| Frequencies for the inductance measurements.                  | The frequencies at<br>which inductance<br>is to be measured.                                                                            | 500 MHz and 2 GHz                                | Any frequency domain<br>test equipment<br>recommended in EIA<br>standards may be used<br>to perform the<br>measurements. If time<br>domain equipment is<br>used, it should have<br>sufficient sampling<br>rates to resolve the<br>specified frequencies.      |                                                                                                                                                                                                                                                       |

| Frequencies for the<br>capacitance<br>measurements.           | The frequencies at<br>which capacitance<br>is to be measured.                                                                           | 500 MHz and 2 GHz                                | Any frequency domain<br>test equipment<br>recommended in EIA<br>standards may be used<br>to perform the<br>measurements. If time<br>domain equipment is<br>used, it should have<br>sufficient sampling<br>rates to resolve the<br>specified frequencies.      |                                                                                                                                                                                                                                                       |

Table 3.

Summary of Required Measurements for the Socket 754 (Continued)